PNR Tool tries to optimize the data path so that data arrival time can be minimized, and the worst negative slack (WNS) and total negative slack (TNS) could be reduced at the placement and optimization stage. Placement is the process of finding a suitable physical location for each cell in the design. The quality of routing in design is highly determined by the placement.

If a greater number of cells are placed in a small area, then the number of routing tracks available for routing is less than the required routing tracks, which may cause congestion in the design. There are several reasons for congestion.

In figure-1 congestions near the port are shown. By applying placement blockages (soft, hard, partial blockage), keep-out margin, Scan chain Reordering, cell padding, macro padding, and creating bounds, the designer must take care of these issues at the beginning. Creating bound allows the user to define region-based placement.

Design Challenges

There are two challenges that would be discussed below: -

- Congestion near the feedthrough port, most of the cells are placed near the port and form a criss-cross path with another port.

- Another challenge is the Reg2out violation. In this case, 48 flip-flops are placed at one location and interact with all macros placed on the left side and the port placed at the left top of the design.

Case 1: fixing congestion

near the feedthrough port

In this section describes a port swapping technique by which congestion can be reduced near the ports. While swapping the port, the designer also has to take care of the other block. If that port of the block is interacting with other blocks, then swapping of the ports will be done accordingly.

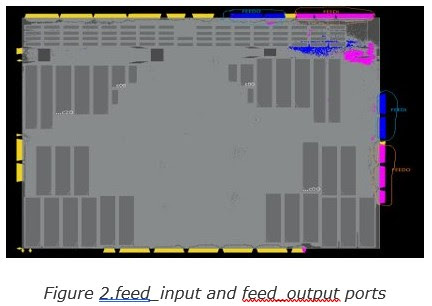

In figure 2, the top ports that are pink in color represent the feed_input ports and feed_output port on the right bottom side. Similarly, for the blue color top right side is feed_output and the right one is the feed_input port. Instances that are highlighted in blue and pink color are registers.

In figure 3, the Top right feed_input ports which are in blue are interacting with the feed_output port which is green in color and is placed on the right edge of the bland we see there are one pipeline registers between them which are shown by the yellow color line.

Implementation:

As shown in figure 4, right-side feed_input* ports are swapped with feed_output* ports to improve congestion by reducing criss-cross near the ports. After implementing this Congestion improved from 4.4% to 2.2%.

Case 2: Fixing Register to

output (REG2OUT) setup violation:

At the floorplan stage,

Macro/IP placement, pin/port placement, and power planning are performed. Only

setup violations would be reported at the placement stage and hold violations

will be reported after the CTS stage PNR flow.

Path groups would be

created for the timing path. This enables reporting the timing results

separately for each group, as well as set the options to focus the timing

optimization on specific critical timing path groups.

Command (in Innovus)

createBasicPathGroups – expanded can be used to create reg2reg, reg2Cgate,

in2reg, reg2out, and in2out path groups.

In the above figure path between flip-flop 1 and flip-flop, 2 is called as reg2reg path, and the path between flip-flop 2 and the output port is called as reg2out path. The reg2reg and reg2cgate default path groups are high effort path groups for optimization and the remaining path groups are low effort, path groups.

We can also create custom path groups according to the requirement. STA person would define constraints for I/O timing e.g. input delay, external delay, etc. in the Synopsys design constraint (SDC) file. Virtual clocks are defined to constrain the I/O timing paths. While doing PnR at the block level, I/O timing should be met even though internal timing has a higher priority.

While doing timing optimization, the

tool will locate flip-flops according to timing requirements. As internal

timing has a higher priority, it might be possible that the tool would place

flip-flops a little away from the I/O port.

METHODOLOGY: -

To fix the IO timing violation, we need to analyze

the cause of the timing violations so that it can be fixed at the right stage.

In this design, reg2out setup violation is reported at the placement stage. The

tool placed those flops a little away from the output port to meet the internal

timing. These violations need to be addressed at the placement stage itself. It

was found that there was enough margin in previous timing paths (reg2reg). So

flopbound could be created near the output port to fix the reg2out setup

violations. Now there are a few things that need to be identified: -

- location of the bound

- Size of the bound

- Which group should be created out of soft Guide, Guide, Region, and Fence?

PNR tool, Innovus support four types of physical

floorplan constraints namely soft guide, guide, region, and fence.

Implementation:

In the design, a region of 48 flops has been created near the output port and it would prevent the spreading of those flops. Hence, reg2out setup violations can be reduced to the desired limit.

Specification of block

|

Dimension |

2126 x 976.68 |

|

Instances |

1.06 M |

|

Utilization |

17% |

|

Macro count |

220 |

In the figure shown above, the output port has been highlighted and the placement

of the registers has been shown before creating the region.

No comments:

Post a Comment