What is POCV?

- POCV stands for Parametric On-Chip Variation. It is an enhanced variation methodology over AOCV.

- POCV advance variation technology provides statistical benefits without expansive statistical library characterization overhead.

- POCV is very effective in technology nodes 20nm and below.

In POCV, instead of applying a specific derating factor to an individual instance, it models delay as a function of a random variable that is specific to that instance.

Delay = Delay (Nominal_Delay) + Delay (Delay_Variation) * P

Where,

P = Standard Normal Variable

Delay_variation (σ) for each cell is obtained through HSPICE simulation and it is a unique value specific to that library cell.

HSPICE = H(Hewlett)-Simulation Program with Integrated Circuit Emphasis; Hspice is a circuit simulator. It can take input circuit description files and produce output files describing the requested simulation.

In normal distribution 68% of data falls within the 1σ range, 95% of data fall within 2σ and 99.7% of data fall within the range of 3σ.

POCV uses a nominal value for modeling random variations on the die instead of using min-max delay values for the timing arc.

POCV analysis uses nominal delay (µ) and variation (σ) for timing analysis in the following way:

- The tool takes the value of σ from the timing library or an external file containing POCV coefficient C.

- Each arc timing is then calculated statistically as the total of the nominal delay and the variation.

- The tool then calculates the delay of the path by statistically combining these arc delays.

By default, the tool performs POCV analysis at three standard deviations (3σ) from the mean.

POCV DATA TYPES:

Single Coefficient (C): An external file contains the coefficients for the delay variations. It applies a single coefficient value C for each library cell, hierarchical cell, or design. The coefficient is the value of the variation at 1 standard deviation from the nominal delay. There is only one value of C for each timing arc of the cell irrespective of the input transition and output load.

Delay variation (σ) = C * Nominal Delay

Below shows an example of POCV coefficient file:

Library Variation Format (LVF):

LVF is an extension to the Library Format (.lib) that adds statistical variations information to timing measurements.

- POCV variation is directly provided in the library itself.

- The variations are loaded in the design by loading the library. It contains the value of variation for multiple slew-load conditions of the cell instead of a single value of C.

- The accuracy of the design at nodes < 16nm is greatly improved.

- Similar to cell delay check, LVF supports POCV coefficients for transition and setup, hold checks as well.

An example of the POCV LVF format has shown below:

A

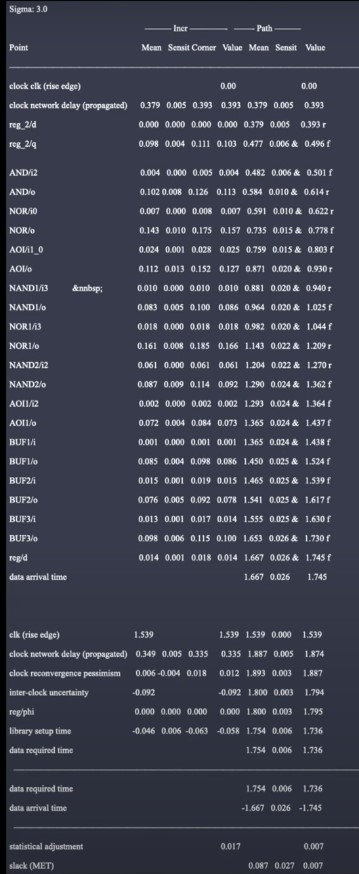

POCV Delay Calculation:

Delay of a cell = Nominal Delay +/- Variation

Delay of a cell = Nominal Delay +/- (C * Nominal Delay) * N

Here, C = POCV coefficient; N = No. of STD deviations

Sensitivity = Mean * POCV coefficient (C)

Corner = Mean +/- (N * sensitivity) ; N = No. of STD deviations

Incr value = Current stage path value – Previous stage path value

Mean for path column = Mean (1st stage) + mean (2nd stage) ….mean (cur stage)

Sensitivity for path column = sqrt [ sens_1st_stg^2 + sens+2nd_stg^2 + …. + sens_cur_stg^2]

Path value = Path mean + (Path sensitivity * N)

For Incr:

Mean = 0.102

Sensit = Mean * C

= 0.102 * 0.0784

= 0.008

Corner = Mean + (N * Sensit)

= 0.102 + (3 * 0.008)

= 0.126

Value = Curr stg value – Prev stg value

= 0.614 – 0.501

= 0.113

For Path:

Mean = 0.379 + 0.000 + 0.098 + 0.004 + 0.102

= 0.584

Sensit = sqrt[(0.006 * 0.006) + (0.008 * 0.008)]

= 0.010

Value = Mean + (Sensit * N)

= 0.584 + (0.010 * 3)

= 0.614

- POCV models random variation.

- Use AOCV derating along with POCV to model systematic variations.

To model non-process-related variations such as voltage and temperature. It applies to both nominal delay and sigma.

When both derates (distance-based and guard band) are present then derate will be the product of the two.

POCV distance derate * POCV guard band

Summary:

In this article POCV has been discussed in detail, The aim of this article is to provide the basic concept of POCV and how to delay calculate using timing report and give a comparative insight.

Thank you!